# ER-TFT101B4-1-5553

### **TFT LCD Module Datasheet**

## **Eastrising Technology Co., Limited**

#### Attention:

- A. Some specifications of IC are not listed in this datasheet. Please refer to the IC datasheet for more details.

- B. The related documents for interfacing, demo code, IC datasheet are all available, please download from our web.

- C. Please pay more attention to "INSPECTION CRITERIA" in this datasheet. We assume you already agree with these criterions when you place an order with us. No more recommendations.

| REV | Description         | Release Date |

|-----|---------------------|--------------|

| 1.0 | Preliminary Release | Jul-25-2024  |

|     |                     |              |

|     |                     |              |

URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 1 of 27

## **CONTENTS**

| 1. | ORDER INFORMATION                                                                                                                                                                                                                                                                                                                                                          | 04                   |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|    | 1.1 Order Number                                                                                                                                                                                                                                                                                                                                                           | 04<br>04             |

|    | 1.3 Controller Board Image                                                                                                                                                                                                                                                                                                                                                 | 05                   |

| 2. | SPECIFICATION                                                                                                                                                                                                                                                                                                                                                              | 06                   |

|    | 2.1 Display Specification                                                                                                                                                                                                                                                                                                                                                  | 06<br>06             |

| 3. | OUTLINE DRAWING                                                                                                                                                                                                                                                                                                                                                            | 07                   |

|    | 3.1 ER-TFT101B4-1-5553 with 4-wire Resistive Touch Panel and Pin Header Connection Outline Drawing 3.2 ER-TFT101B4-1-5553 with 4-wire Resistive Touch Panel and FFC Connection Outline Drawing 3.3 ER-TFT101B4-1-5553 with Capacitive Touch Panel and FFC Connection Outline Drawing 3.4 ER-TFT101B4-1-5553 with Capacitive Touch Panel and FFC Connection Outline Drawing | 07<br>08<br>09<br>10 |

| 4. | ELECTRICAL SPEC                                                                                                                                                                                                                                                                                                                                                            | 11                   |

|    | 4.1 Pin Configuration-JP1/CON1                                                                                                                                                                                                                                                                                                                                             |                      |

|    | 4.2 Pin Configuration-JP2/CON2 (Micro SD Card interface)                                                                                                                                                                                                                                                                                                                   |                      |

|    | 4.4 Jump Point Description                                                                                                                                                                                                                                                                                                                                                 |                      |

|    | 4.5 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                               |                      |

|    | 4.6 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                             | 14                   |

| 5. | INSPECTION CRITERIA                                                                                                                                                                                                                                                                                                                                                        | 15                   |

|    | 5.1 Acceptable Quality Level                                                                                                                                                                                                                                                                                                                                               |                      |

|    | 5.2 Definition of Lot                                                                                                                                                                                                                                                                                                                                                      |                      |

|    | 5.3 Condition of Cosmetic Inspection                                                                                                                                                                                                                                                                                                                                       |                      |

|    | 5.4 Module Cosmetic Criteria                                                                                                                                                                                                                                                                                                                                               |                      |

|    | 5.5 Screen Cosmetic Criteria (Non-Operating)                                                                                                                                                                                                                                                                                                                               |                      |

|    | 5.6 Screen Cosmetic Criteria (Operating)                                                                                                                                                                                                                                                                                                                                   | 19                   |

URL: <a href="https://www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 2 of 27

URL: www.buydisplay.com

| 6. PRECAUTIONS FOR USING                                  | <br>21 |

|-----------------------------------------------------------|--------|

| 6.1 Handling Precautions                                  | <br>21 |

| 6.2 Power Supply Precautions                              | <br>21 |

| 6.3 Operating Precautions                                 | <br>22 |

| 6.4 Mechanical/Environmental Precautions                  | <br>22 |

| 6.5 Storage Precautions                                   | <br>22 |

| 6.6 Others                                                | <br>22 |

| 7.USING LCD MODULES                                       | <br>23 |

| 7.1 Liquid Crystal Display Modules                        | <br>23 |

| 7.2 Installing LCD Modules                                | <br>23 |

| 7.3 Precaution for Handling LCD Modules                   | <br>23 |

| 7.4 Electro-Static Discharge Control                      | <br>24 |

| 7.5 Precaution for Soldering to Eastrising LCM            | <br>24 |

| 7.6 Precaution for Operation                              | <br>24 |

| 7.7 Limited Warranty                                      | <br>25 |

| 7.8 Return Policy                                         | <br>25 |

| 8. IMAGE STICKING                                         | <br>26 |

| 8.1 What is Image Sticking?                               | <br>26 |

| 8.2 What causes Image Sticking?                           | <br>26 |

| 8.3 How to Avoid Image Sticking?                          | <br>27 |

| 8.4 How to Fix the Image Sticking?                        | <br>27 |

| 8.5 Is Image Sticking Covered by Eastrising RMA Warranty? | <br>27 |

Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 3 of 27

### 1. ORDERING INFORMATION

#### 1.1 Order Number

| Order Number            | Description                                                    |

|-------------------------|----------------------------------------------------------------|

| ER-TFT101B4-1-5553      | 10.1" IPS TFT LCD Display with LT7683(RA8876) Controller Board |

| ER-TP101-1              | 10.1" Resistive Touch Panel                                    |

| ER-TPC101-1             | 10.1" Capacitive Touch Panel                                   |

| ER-TFT101B4-1-5553-5571 | Arduino Shield                                                 |

### 1.2 Display Image

- ER-TFT101B4-1-5553 with No Touch Panel

ER-TFT101B4-1-5553 with Resistive Touch Panel →

← ER-TFT101B4-1-5553 with Capacitive Touch Panel

Page: 4 of 27 URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553\_Datasheet

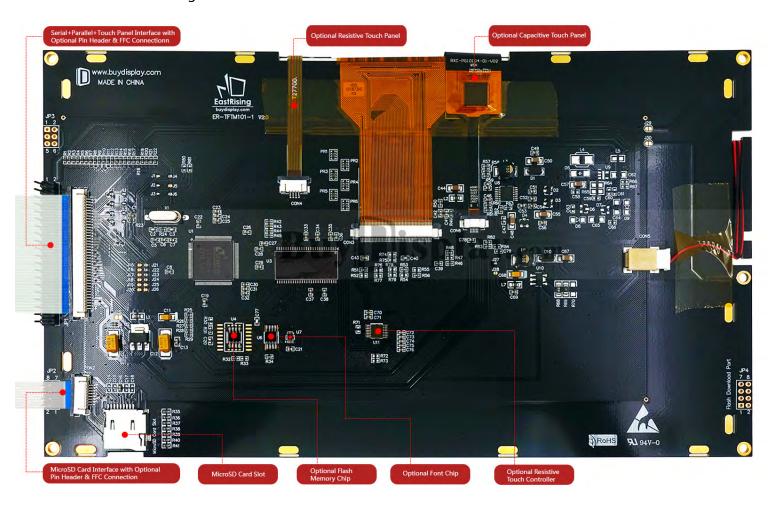

### 1.3 Controller Board Image

URL: <a href="https://www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 5 of 27

### 2. SPECIFICATION

### 2.1 Display Specification

| Item                  | Standard Value    | Unit   |

|-----------------------|-------------------|--------|

| Display Format        | 1024x600          | Pixels |

| Display Connector     | FFC or Pin Header |        |

| Operating Temperature | -20 ~ +70         | ℃      |

| Storage Temperature   | -30 ~ +80         | ℃      |

| Touch Panel Optional  | Yes               |        |

| Sunlight Readable     | No                |        |

### 2.2 Mechanical Specification

| Item                    | Standard Value      | Unit |

|-------------------------|---------------------|------|

| Diagonal Size           | 10.1                | Inch |

| Outline Dimension (PCB) | 248.50(W)x145.50(H) | mm   |

| Visual Area             | 226.40(W)x128.70(H) | mm   |

| Active Area             | 222.72(W)x125.28(H) | mm   |

| Dot Pitch               | 0.217x0.208         | mm   |

### 2.3 Electrical Specification

| Item                | Standard Value                                          | Unit |

|---------------------|---------------------------------------------------------|------|

| IC Package          | SMT                                                     |      |

| Controller          | RA8876 or LT7683                                        |      |

| Interface           | 8080/6800 8-bit/16-bit Parallel, 3-wire,4-wire SPI ,I2C |      |

| Response Time (Typ) | 20                                                      | MS   |

### 2.4 Optical Specification

| Item                 | Standard Value                       | Unit  |

|----------------------|--------------------------------------|-------|

| LCD Type             | IPS                                  |       |

| Viewing Angle Range  | Left:80 , Right:80 , Up:80 , Down:80 | Deg   |

| Colors               | 65k/262k/16.7M                       |       |

| Contrast Ratio (Typ) | 800:1                                |       |

| Brightness (Typ)     | 600                                  | cd/m2 |

URL: <a href="https://www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 6 of 27

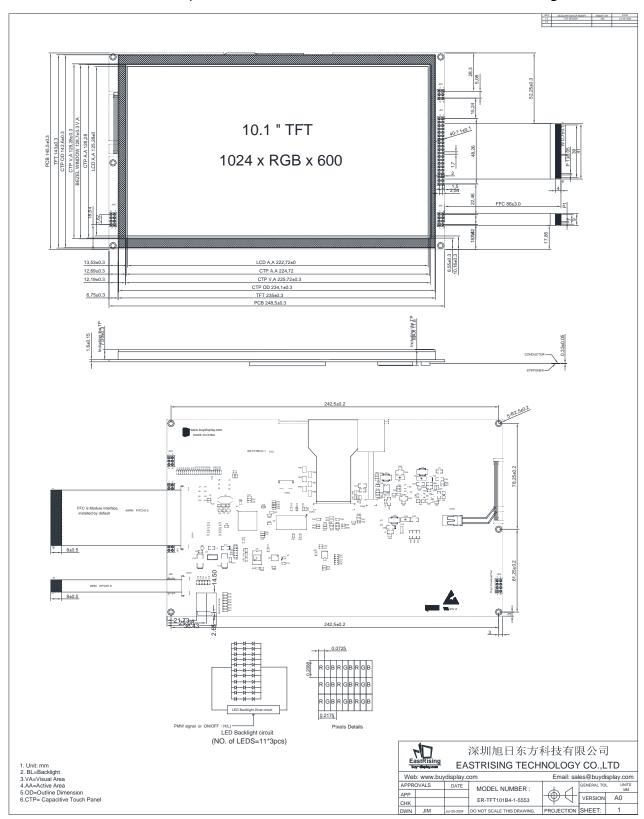

### 3. OUTLINE DRAWING

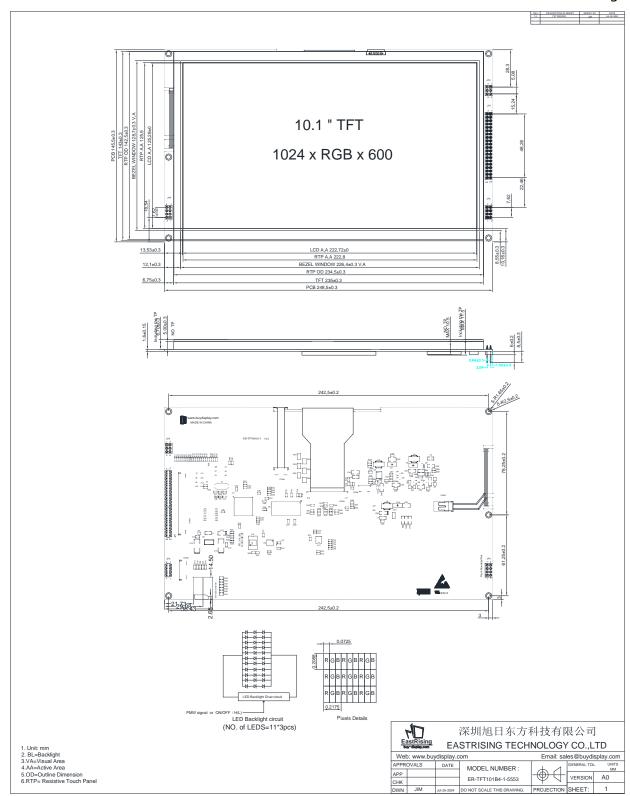

3.1 ER-TFT101B4-1-5553 with 4-wire Resistive Touch Panel and Pin Header Connection Outline Drawing

URL: <a href="https://www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 7 of 27

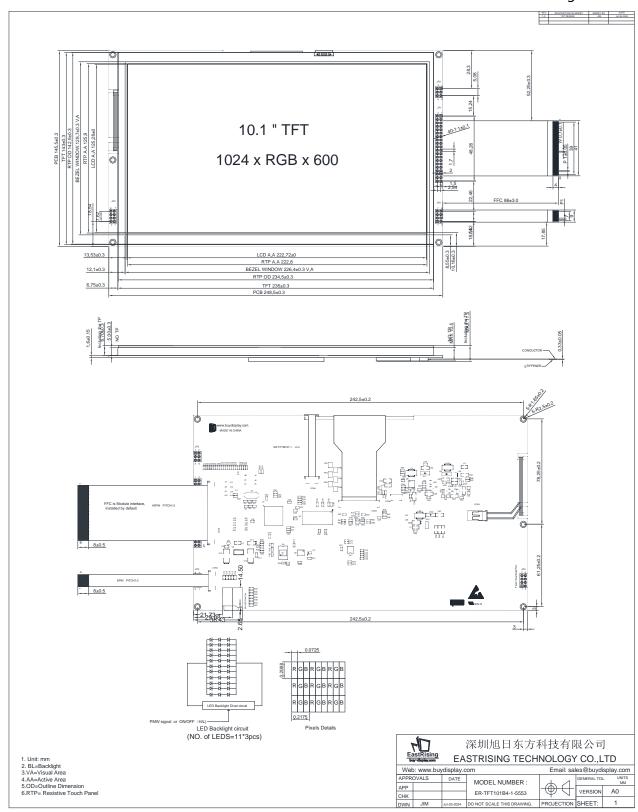

### 3.2 ER-TFT101B4-1-5553 with 4-wire Resistive Touch Panel and FFC Connection Outline Drawing

### 3.3 ER-TFT101B4-1-5553 with Capacitive Touch Panel and Pin Header Connection Outline Drawing

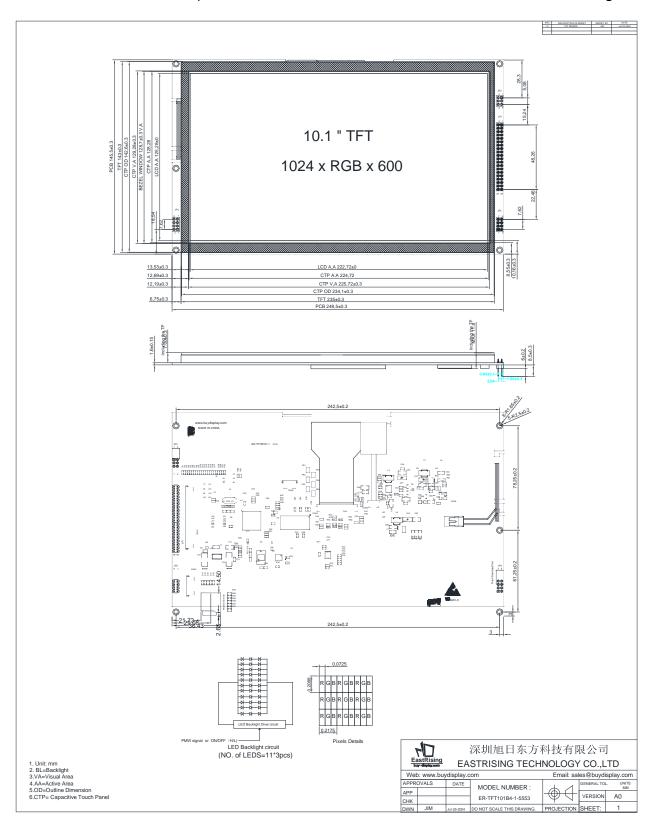

### 3.4 ER-TFT101B4-1-5553 with Capacitive Touch Panel and FFC Connection Outline Drawing

### 4. ELECTRICAL SPEC

4.1 Pin Configuration-JP1/CON1 (Parallel+Serial+Touch Panel Interface)

| Pin No | Symbol        | Descriptions                                                                             |  |

|--------|---------------|------------------------------------------------------------------------------------------|--|

| 1      | VSS           | Ground                                                                                   |  |

| 2      | VSS           | Ground                                                                                   |  |

| 3      | VDD           | Power Supply                                                                             |  |

| 4      | VDD           | Power Supply                                                                             |  |

|        |               | Enable/Read Enable                                                                       |  |

|        | Parallel Mode | When MCU interface (I/F) is 8080 series, this pin is used as RD# signal                  |  |

|        | E_/RD         | (Data Read) , active low.                                                                |  |

|        |               | When MCU I/F is 6800 series, this pin is used as EN signal (Enable), active high         |  |

| 5      |               |                                                                                          |  |

|        | Serial Mode   | Serial Mode Chip Select, Low active chip select pin.                                     |  |

|        | /SCS          | Chip select pin for 3-Wire , 4-wire serial .                                             |  |

|        | , , , ,       | XI2CA[4], I2C device address bit [4],internal pull-high, jumper J19.                     |  |

|        |               | Write/Read-Write                                                                         |  |

|        | Parallel Mode | When MCU interface is 8080 series, this pin is used as WR# signal (data                  |  |

|        | R/W_/WR       | write) , active low.                                                                     |  |

|        |               | When MCU interface is 6800 series, this pin is used as RW# signal (data                  |  |

| 6      |               | Read/Write control) . Active high for read and active low for write.                     |  |

|        | Carial Mada   | 4-wire SPI interface: SDO. Data output.                                                  |  |

|        | Serial Mode   | 3-wire SPI interface: SDA. Bi-direction data.                                            |  |

|        | SDO           | IIC interface: I2C device address bit [5], internal pull-high, jumper J20.               |  |

|        | Parallel Mode | Parallel Mode Chip Select Input                                                          |  |

|        | /CS           | Low active chip select pin.                                                              |  |

|        |               | Low active crip select piri.                                                             |  |

| 7      |               | IIC data /4-wire SPI Data Input                                                          |  |

|        | Serial Mode   | 4-wire SPI interface: SDI. Data input for serial interface                               |  |

|        | SDI           | 3-wire SPI interface: NC, please connect it to GND.                                      |  |

|        |               | IIC interface: SDA. Bi-direction data.                                                   |  |

|        | Parallel Mode | Command / Data Select Input                                                              |  |

|        | RS            | The pin is used to select data/command cycle. RS = 1, data Read/Write cycle is selected. |  |

| 8      |               | RS = 0, status read/command write cycle is selected.                                     |  |

|        | Serial Mode   | SPI Clock                                                                                |  |

|        | SCLK          | 3-wire, 4-wire Serial or IIC interface clock                                             |  |

|        |               | Wait Signal Output                                                                       |  |

| 9      | WAIT          | When high, it indicates that the LT7683 is ready to transfer data. When low,then         |  |

|        |               | microprocessor is in wait state.                                                         |  |

| 10     | INT           | Interrupt Signal Output                                                                  |  |

| 10     | 11.4.1        | The interrupt output for MCU to indicate the status.                                     |  |

URL: <a href="https://www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 11 of 27

buydisplay.com

| <u> </u> | <u> </u>   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 11       | /RESET     | This is bidirectional power-on reset input/output. Output is open collector.  While internal POR active, this pin will output internal reset event (active low).  If internal reset event finish, this pin becomes input mode and accept external reset event (active low). Before User start access the chip via MPU interface, user should wait at least 256 OSC clocks and then must check status register to make sure internal reset is finished.  To avoid noise interfere XRST signal and cause fake reset behavior, external XRST level will be admitted only if it keep its signal level at least 256 OSC clocks. |  |

| 12       | NC         | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 13       | VSS        | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 14       | BL CONTROL | Backlight control signal input. When using the internal PWM signal this pin floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 15-30    | DB0-DB15   | Data Bus.  These are data bus for data transfer between parallel host and LT7683.  XDB[15:8] will become GPIO (GPIO-A[7:0]) if parallel host 8080/6800 16-bits data bus mode doesn' t set.  XDB[7:0] are multiplex with serial host signals if serial host mode set. Please refer to serial host interface section.                                                                                                                                                                                                                                                                                                        |  |

| 31       | VSS        | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 32       | RTP_/CS    | Chip Select Input. Active Low Logic Input. This input provides the dual function of initiating conversions on the XPT2046 and also enables the serial input/output register.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 22       | RTP_/PEN   | Pen Interrupt. CMOS logic open-drain output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 33       | CTP_INT    | An interrupt signal to inform the host processor that touches data is ready for read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 34       | RTP_DIN    | Data In. Logic input. Data to be written to the XPT2046 control register is provided on this input and is clocked into the register on the rising edge of DCLK (see the Control Register section).                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|          | CTP_SDA    | Serial data input/ Output(I2C).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 35       | RTP_SCLK   | External Clock Input. Logic Input. DCLK provides the serial clock for accessing data from the part. This clock input is also used as the clock source for the XPT2046 conversion process.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|          | CTP_SCL    | Serial clock input (I2C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 36       | RTP_DOUT   | Data Out. Logic Output. The conversion result from the XPT2046 is provided on this output as a serial data stream. The bits are clocked out on the falling edge of the DCLK input. This output is high impedance when CS is high.                                                                                                                                                                                                                                                                                                                                                                                          |  |

|          | CTP_/RST   | External low signal reset the chip. RC reset circuit on Board, this pin can be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 37       | VDD        | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 38       | VDD        | Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 39       | VSS        | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|          | 1          | ļ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

URL: <a href="https://www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 12 of 27

| 40 | S | Ground |

|----|---|--------|

|----|---|--------|

Note: CTP means Capacitive Touch Panel. RTP means 4-wire Resistive Touch Panel.

### 4.2 Pin Configuration-JP2/CON2 (Micro SD Card interface)

| SD Mode |                | SPI Mode | SPI Mode       |  |  |

|---------|----------------|----------|----------------|--|--|

| Pin No  | SIGNAL         | Pin No   | Symbol         |  |  |

| 1       | DATA2          | 1        | NC             |  |  |

| 2       | DATA3          | 2        | /CS            |  |  |

| 3       | CMD            | 3        | DIN            |  |  |

| 4       | CLK            | 4        | SCLK           |  |  |

| 5       | GND            | 5        | GND            |  |  |

| 6       | DATA0          | 6        | DOUT           |  |  |

| 7       | DATA1          | 7        | NC             |  |  |

| 8       | CARD DETECTION | 8        | CARD DETECTION |  |  |

### 4.3 JP3 Description (Flash Download Port)

| Pin<br>No | Symbol | Descriptions           |

|-----------|--------|------------------------|

| 1         | VDD    | Flash VDD Input (3.3V) |

| 2         | VSS    | Ground                 |

| 3         | /WP    | Write Protect          |

| 4         | /HOLD  | HOLD Signal.           |

| 5         | DOUT   | MISO.                  |

| 6         | /CS    | Chip Select.           |

| 7         | DIN    | MOSI                   |

| 8         | SCLK   | Clock Input            |

### 4.4 Jump Point Description

| Function Description    | Jump Method                                         |

|-------------------------|-----------------------------------------------------|

| Davier Cumply Cuitch    | Vdd=3.3V Power Supply : J29 Short                   |

| Power Supply Switch     | Vdd=5V Power Supply : J29 Open                      |

| 8080 Parallel Interface | J1,J2,J3,J11,J12,J13,J14 Short                      |

| 6000 Parallel Interface | J4,J5,J6,J7,J8,J9,J10,J15-J26 Open                  |

| 6800 Parallel Interface | J1,J3,J5,J11,J12,J13,J14 Short                      |

| 6000 Parallel Interface | J2,J4,J6,J7,J8,J9,J10,J15-J26 Open                  |

| I2C Interface           | J4,J5,J6,J7,J8,J9,J10,J15,J16,J17,J18,J19,J20 Short |

| 12C Interface           | J1,J2,J3,J11,J12,J13,J14,J21-J26 Open               |

| 3-wire Serial Interface | J1,J2,J6,J7,J8,J9,J10,J21,J22,J23,J24 Short         |

| 5-wire Serial Interface | J3,J4,J5,J11,J12,J13,J14,J15-J20,J25,J26 Open       |

| 4-wire Serial Interface | J2,J4,J6,J7,J8,J9,J10,J21,J22,J23,J24 Short         |

| 4-wire Serial interface | J1,J3,J5,J11,J12,J13,J14,J15-J20,J25,J26 Open       |

URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 13 of 27

buydisplay.com

| Packlight Control | J27 Short,J28 Open: Select Backlight Control Signal with External Input |

|-------------------|-------------------------------------------------------------------------|

| Backlight Control | J27 Open,J28 Short: Select Backlight Control Signal with RA8876'PWM     |

Note: We set 8080 interface, 5V power supply, Backlight external control by default.

### 4.5 Absolute Maximum Ratings

| Item                 | Symbol | Min  | Тур | Max          | Unit |

|----------------------|--------|------|-----|--------------|------|

| Power Supply Voltage | VDD    | -0.5 | -   | +4           | V    |

| Logic Signal Voltage | VDDIO  | -0.5 | -   | +3.3         | V    |

| Humidity             | RH     | -    |     | 90%(Max60°C) | RH   |

### 4.6 Electrical Characteristics

| Item                      | Symbol    | Min. | Тур. | Max. | Unit |

|---------------------------|-----------|------|------|------|------|

| Dower Supply Voltage (*1) | VDD       | 3.3  | 3.3  | 3.6  | V    |

| Power Supply Voltage(*1)  |           | 4.8  | 5.0  | 5.5  | V    |

| Logic Signal I/O Voltage  | VDDIO     | 3.0  | 3.3  | 3.6  | V    |

| Input Voltage 'H' Level   | VIH       | 2.0  | -    | 3.6  | V    |

| Input Voltage 'L' Level   | VIL       | -0.3 | -    | 0.8  | V    |

| Output Voltage 'H' Level  | VOH       | 2.4  | -    | 3.6  | V    |

| Output Voltage 'L' Level  | VCL       | 0    | -    | 0.4  | V    |

| Module Current            | IDD(3.3V) |      |      | 1000 | mA   |

| iviodule Current          | IDD(5.0V) |      |      | 650  | mA   |

Note1: Short J22 if VDD=3.3V

URL: <a href="https://www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 14 of 27

### 5. INSPECTION CRITERIA

### 5.1 Acceptable Quality Level

Each lot should satisfy the quality level defined as follows

| Partition | AQL  | Definition                                                         |

|-----------|------|--------------------------------------------------------------------|

| A. Major  | 0.4% | Functional defective as product                                    |

| B. Minor  | 1.5% | Satisfy all functions as product but not satisfy cosmetic standard |

#### 5.2 Definition of Lot

One lot means the delivery quantity to customer at one time.

- 5.3 Condition of Cosmetic Inspection

- INSPECTION AND TEST

- -FUNCTION TEST

- -APPEARANCE INSPECTION

- -PACKING SPECIFICTION

- INSPECTION CONDITION

- Put under the lamp (20W) at a distance 100mm from

- Tilt upright 45 degree by the front (back) to inspect LCD appearance.

- AQL INSPECTION LEVEL

- SAMPLING METHOD: MIL-STD-105D

- SAMPLING PLAN: SINGLE

- MAJOR DEFECT: 0.4% (MAJOR)

MINOR DEFECT: 1.5% (MINOR)

- GENERAL LEVEL: II/NORMAL

URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 15 of 27

### 5.4 Module Cosmetic Criteria

| No. | ltem                       | Judgment Criterion                                                                                                                                                                                    | Partition |

|-----|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 1   | Difference in Spec.        | None allowed                                                                                                                                                                                          | Major     |

| 2   | Pattern Peeling            | No substrate pattern peeling and floating                                                                                                                                                             | Major     |

| 3   | Soldering Defects          | No soldering missing                                                                                                                                                                                  | Major     |

|     |                            | No soldering bridge                                                                                                                                                                                   | Major     |

|     |                            | No cold soldering                                                                                                                                                                                     | Minor     |

| 4   | Resist Flaw on Substrate   | Invisible copper foil( ¢ 0.5mm or more)on substrate pattern                                                                                                                                           | Minor     |

| 5   | Accretion of Metallic      | No soldering dust                                                                                                                                                                                     | Minor     |

|     | Foreign Matter             | No accretion of metallic foreign matters(Not exceed ¢ 0.2mm)                                                                                                                                          |           |

| 6   | Stain                      | No stain to spoil cosmetic badly                                                                                                                                                                      | Minor     |

| 7   | Plate Discoloring          | No plate fading, rusting and discoloring                                                                                                                                                              | Minor     |

| 8   | Solder Amount 1.Lead Parts | a. Soldering side of PCB  Solder to form a' Filet' all around t  Solder should not hide the lead form  b.Components side  (In case of 'Through Hole PCB')  Solder to reach the Components side of PCB | Minor     |

| 8   | 2.Flat Packages 3.Chips    | Either 'toe' (A) or 'heal' (B) of the lead to be covered by Filet'  Lead form to be assume over solder.  (3/2) H≥h≥(1/2)H                                                                             | Minor     |

Page: 16 of 27 URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553\_Datasheet

buydisplay.com

| 9  | Backlight Defects | 1.Light fails or flickers.(Major)                                  |       |

|----|-------------------|--------------------------------------------------------------------|-------|

|    |                   | 2. Color and luminance do not correspond to specifications.        | See   |

|    |                   | (Major)                                                            | list  |

|    |                   | 3.Exceeds standards for display's blemishes, foreign matter,       | ←     |

|    |                   | dark lines or scratches.(Minor)                                    |       |

| 10 | PCB Defects       | Oxidation or contamination on connectors.*                         |       |

|    |                   | 2. Wrong parts, missing parts, or parts not in specification.*     |       |

|    |                   | 3.Jumpers set incorrectly.(Minor)                                  | See   |

|    |                   | 4.Solder(if any)on bezel, LED pad, zebra pad, or screw hole        | list  |

|    |                   | pad is not smooth.(Minor)                                          | ←     |

|    |                   | *Minor if display functions correctly. Major if the display fails. |       |

| 11 | Soldering Defects | 1. Unmelted solder paste.                                          | Minor |

|    |                   | 2. Cold solder joints, missing solder connections, or oxidation.*  |       |

|    |                   | 3. Solder bridges causing short circuits.*                         |       |

|    |                   | 4. Residue or solder balls.                                        |       |

|    |                   | 5. Solder flux is black or brown.                                  |       |

|    |                   | *Minor if display functions correctly. Major if the display fails. |       |

URL: <a href="https://www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 17 of 27

### 5.5 Screen Cosmetic Criteria (Non-Operating)

| No. | Defect               | Judgment Criterion                                                     | Partition                                  |       |

|-----|----------------------|------------------------------------------------------------------------|--------------------------------------------|-------|

| 1   | Spots                | In accordance with Screen Cosmetic                                     | Criteria (Operating) No.1.                 | Minor |

| 2   | Lines                | In accordance with Screen Cosmetic                                     | Criteria (Operation) No.2.                 | Minor |

| 3   | Bubbles in Polarizer |                                                                        |                                            | Minor |

|     |                      | Size: d mm                                                             | Acceptable Qty in active area              |       |

|     |                      | d≦0.3                                                                  | Disregard                                  |       |

|     |                      | 0.3 < d≦1.0                                                            | 3                                          |       |

|     |                      | 1.0 <d≦1.5< td=""><td>1</td><td></td></d≦1.5<>                         | 1                                          |       |

|     |                      | 1.5 < d                                                                | 0                                          |       |

|     |                      |                                                                        |                                            |       |

|     |                      |                                                                        |                                            |       |

| 4   | Scratch              | In accordance with spots and lines of                                  | perating cosmetic criteria, When the light | Minor |

|     |                      | reflects on the panel surface, the scra                                | atches are not to be remarkable.           |       |

| 5   | Allowable density    | Above defects should be separated r                                    | Minor                                      |       |

| 6   | Coloration           | Not to be noticeable coloration in the viewing area of the LCD panels. |                                            | Minor |

|     |                      | Back-lit type should be judged with b                                  |                                            |       |

| 7   | Contamination        | Not to be noticeable.                                                  |                                            | Minor |

Page: 18 of 27 URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553\_Datasheet

## 5.6 Screen Cosmetic Criteria (Operating)

| No. | Defect | Judgmer                                        | nt Criterion                        | Partition |

|-----|--------|------------------------------------------------|-------------------------------------|-----------|

| 1   | Spots  | A) Clear                                       |                                     | Minor     |

|     |        | Size:d mm                                      | Acceptable Qty in active area       |           |

|     |        | d≦0.1                                          | Disregard                           |           |

|     |        | 0.1 <d≦0.2< td=""><td>6</td><td></td></d≦0.2<> | 6                                   |           |

|     |        | 0.2 <d≦0.3< td=""><td>2</td><td></td></d≦0.3<> | 2                                   |           |

|     |        | 0.3 <d< td=""><td>0</td><td></td></d<>         | 0                                   |           |

|     |        | Note: Including pin holes and defective Size.  | dots which must be within one pixel |           |

|     |        | Unclear                                        |                                     |           |

|     |        | Size:d mm                                      | Acceptable Qty in active area       |           |

|     |        | d≦0.2                                          | Disregard                           |           |

|     |        | 0.2 <d≦0.5< td=""><td>6</td><td></td></d≦0.5<> | 6                                   |           |

|     |        | 0.5 <d≦0.7< td=""><td>2</td><td></td></d≦0.7<> | 2                                   |           |

|     |        | 0.7 <d< td=""><td>0</td><td></td></d<>         | 0                                   |           |

| 2   | Lines  | A) Clear  L 5.0 2.0  0.02  0.05                | See No.1 0.1                        | Minor     |

|     |        | Note: () – Acceptable Qty in active area       |                                     |           |

|     |        | L - Length (mm)                                |                                     |           |

|     |        | W -Width(mm)                                   |                                     |           |

|     |        | ∞-Disregard                                    |                                     |           |

|     |        | B) Unclear                                     |                                     |           |

|     |        | L 10.0   ∞ (6)                                 | (0)                                 |           |

|     |        | 0.05                                           | See No.1<br>W                       |           |

Clear' = The shade and size are not changed by Vo.

Unclear' = The shade and size are changed by Vo.

URL: <a href="https://www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 19 of 27

| No. | Defect                                  | Judgment Criterion                                                                                                                                                                                                                                                                                                                                           | Partition |

|-----|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3   | Rubbing line                            | Not to be noticeable.                                                                                                                                                                                                                                                                                                                                        | Minor     |

| 4   | Allowable density                       | Above defects should be separated more than 10mm each other.                                                                                                                                                                                                                                                                                                 | Minor     |

| 5   | Rainbow                                 | Not to be noticeable.                                                                                                                                                                                                                                                                                                                                        | Minor     |

| 6   | Dot size                                | To be 95%~105% of the dot size (Typ.) in drawing.  Partial defects of each dot (ex.pin-hole) should be treated as spot.  (see Screen Cosmetic Criteria (Operating) No.1)                                                                                                                                                                                     | Minor     |

| 7   | Brightness<br>(only back-lit<br>Module) | Brightness Uniformity must be BMAX/BMIN≤2  - BMAX : Max.value by measure in 5 points  - BMIN : Min.value by measure in 5 points  Divide active area into 4 vertically and horizontally.  Measure 5 points shown in the following figure.                                                                                                                     | Minor     |

| 8   | Contrast Uniformity                     | Contrast Uniformity must be BmAX/BMIN≦2  Measure 5 points shown in the following figure.  Dashed lines divide active area into 4 vertically and horizontally.  Measuring points are located at the inter-sections of dashed line.  Note: BMAX – Max.value by measure in 5 points.  BMIN – Min.value by measure in 5 points.  O – Measuring points in ¢ 10mm. | Minor     |

#### Note:

- (1) Size: d=(long length + short length)/2

- (2) The limit samples for each item have priority.

- (3) Complexed defects are defined item by item, but if the number of defects is defined in above table, the total number should not exceed 10.

URL: <a href="www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 20 of 27

(4) In case of 'concentration', even the spots or the lines of 'disregarded' size should not be allowed. Following three situations should be treated as 'concentration'.

- -7 or over defects in circle of \$5mm.

- -10 or over defects in circle of \$10mm

- -20 or over defects in circle of ¢20mm

#### 6. PRECAUTIONS FOR USING

### 6.1 Handling Precautions

- This device is susceptible to Electro-Static Discharge (ESD) damage. Observe Anti-Static precautions.

- Eastrising display panel is made of glass. Do not subject it to a mechanical shock by dropping it or impact.

- If Eastrising display panel is damaged and the liquid crystal substance leaks out, be sure not to get any in your mouth. If the substance contacts your skin or clothes, wash it off using soap and water.

- Do not apply excessive force to the Eastrising display surface or the adjoining areas since this may cause the color tone to

- The polarizer covering the Eastrising display surface of the LCD module is soft and easily scratched. Handle this polarizer

- If Eastrising display surface becomes contaminated, breathe on the surface and gently wipe it with a soft dry cloth. If it is heavily contaminated, moisten cloth with one of the following Isopropyl or alcohol.

- Solvents other than those above-mentioned may damage the polarizer. Especially, do not use the Water.

- Exercise care to minimize corrosion of the electrode. Corrosion of the electrodes is accelerated by water droplets, moisture condensation or a current flow in a high-humidity environment.

- Install the Eastrising LCD Module by using the mounting holes. When mounting the LCD module make sure it is free of twisting, warping and distortion. In particular, do not forcibly pull or bend the cable or the backlight cable.

- Do not attempt to disassemble or process Eastrising LCD module.

- NC terminal should be open. Do not connect anything.

- If the logic circuit power is off, do not apply the input signals.

- To prevent destruction of the elements by static electricity, be careful to maintain an optimum work environment.

- -Be sure to ground the body when handling Eastrising LCD modules.

- -Tools required for assembling, such as soldering irons, must be properly grounded.

- -To reduce the amount of static electricity generated, do not conduct assembling and other work under dry conditions.

- -The LCD module is coated with a film to protect the display surface. Exercise care when peeling off this protective film since static electricity may be generated.

### 6.2 Power Supply Precautions

- Identify and, at all times, observe absolute maximum ratings for both logic and LC drivers. Note that there is some variance between models.

- Prevent the application of reverse polarity to VDD and VSS, however briefly.

- Use a clean power source free from transients. Power-up conditions are occasionally jolting and may exceed the maximum ratings of Eastrising modules.

- The VDD power of Eastrising module should also supply the power to all devices that may access the display. Don' t allow the data bus to be driven when the logic supply to the module is turned off.

URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553 Datasheet Page: 21 of 27

6.3 Operating Precautions

- DO NOT plug or unplug Eastrising module when the system is powered up.

- Minimize the cable length between Eastrising module and host MPU.

- For models with backlights, do not disable the backlight by interrupting the HV line. Unload inverters produce voltage extremes that may arc within a cable or at the display.

- Operate Eastrising module within the limits of the modules temperature specifications.

#### 6.4 Mechanical/Environmental Precautions

- Improper soldering is the major cause of module difficulty. Use of flux cleaner is not recommended as they may seep under the electrometric connection and cause display failure.

- Mount Eastrising module so that it is free from torque and mechanical stress.

- Surface of the LCD panel should not be touched or scratched. The display front surface is an easily scratched, plastic polarizer. Avoid contact and clean only when necessary with soft, absorbent cotton dampened with petroleum benzene.

- Always employ anti-static procedure while handling Eastrising module.

- Prevent moisture build-up upon the module and observe the environmental constraints for storage tem

- Do not store in direct sunlight

- If leakage of the liquid crystal material should occur, avoid contact with this material, particularly ingestion. If the body or clothing becomes contaminated by the liquid crystal material, wash thoroughly with water and soap.

### **6.5 Storage Precautions**

When storing the LCD modules, avoid exposure to direct sunlight or to the light of fluorescent lamps.

Keep Eastrising modules in bags (avoid high temperature / high humidity and low temperatures below 0 °C.

Whenever possible, Eastrising LCD modules should be stored in the same conditions in which they were shipped from our company.

#### 6.6 Others

Liquid crystals solidify under low temperature (below the storage temperature range) leading to defective orientation or the generation of air bubbles (black or white). Air bubbles may also be generated if the module is subject to a low temperature. If Eastrising LCD modules have been operating for a long time showing the same display patterns, the display patterns may remain on the screen as ghost images and a slight contrast irregularity may also appear. A normal operating status can be regained by suspending use for some time. It should be noted that this phenomenon does not adversely affect performance reliability.

To minimize the performance degradation of the LCD modules resulting from destruction caused by static electricity etc., exercise care to avoid holding the following sections when handling the modules.

- -Exposed area of the printed circuit board.

- -Terminal electrode sections.

URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 22 of 27

### 7. USING LCD MODULES

#### 7.1 Liquid Crystal Display Modules

Eastrising LCD is composed of glass and polarizer. Pay attention to the following items when handling.

- Please keep the temperature within specified range for use and storage. Polarization degradation, bubble generation or polarizer peel-off may occur with high temperature and high humidity.

- Do not touch, push or rub the exposed polarizers with anything harder than an HB pencil lead (glass, tweezers, etc.).

- N-hexane is recommended for cleaning the adhesives used to attach front/rear polarizers and reflectors made of organic substances which will be damaged by chemicals such as acetone, toluene, ethanol and isopropyl alcohol.

- When Eastrising display surface becomes dusty, wipe gently with absorbent cotton or other soft material like chamois soaked in petroleum benzin. Do not scrub hard to avoid damaging the display surface.

- Wipe off saliva or water drops immediately, contact with water over a long period of time may cause deformation or color fading.

- Avoid contacting oil and fats.

- Condensation on the surface and contact with terminals due to cold will damage, stain or dirty the polarizers. After products are tested at low temperature they must be warmed up in a container before coming is contacting with room temperature air.

- Do not put or attach anything on Eastrising display area to avoid leaving marks on.

- Do not touch the display with bare hands. This will stain the display area and degradate insulation between terminals (some cosmetics are determinated to the polarizers).

- As glass is fragile. It tends to become or chipped during handling especially on the edges. Please avoid dropping.

#### 7.2 Installing LCD Modules

- Cover the surface with a transparent protective plate to protect the polarizer and LC cell.

- When assembling the LCM into other equipment, the spacer to the bit between the LCM and the fitting

plate should have enough height to avoid causing stress to the module surface, refer to the individual specifications for

measurements. The measurement tolerance should be±0.1mm.

#### 7.3 Precaution for Handling LCD Modules

Since Eastrising LCM has been assembled and adjusted with a high degree of precision; avoid applying excessive shocks to the module or making any alterations or modifications to it.

- Do not alter, modify or change the shape of the tab on the metal frame.

- Do not make extra holes on the printed circuit board, modify its shape or change the positions of components to be attached.

- Do not damage or modify the pattern writing on the printed circuit board.

- Absolutely do not modify the zebra rubber strip (conductive rubber) or heat seal connector.

- Except for soldering the interface, do not make any alterations or modifications with a soldering iron.

- Do not drop, bend or twist Eastrising LCM.

URL: <a href="www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 23 of 27

### 7.4 Electro-Static Discharge Control

Since this module uses a CMOS LSI, the same careful attention should be paid to electrostatic discharge as for an ordinary CMOS IC.

- Make certain that you are grounded when handing LCM.

- Before remove LCM from its packing case or incorporating it into a set, be sure the module and your body have the same electric potential.

- When soldering the terminal of LCM, make certain the AC power source for the soldering iron does not leak.

- When using an electric screwdriver to attach LCM, the screwdriver should be of ground potentiality to minimize as much as possible any transmission of electromagnetic waves produced sparks coming from the commutator of the motor.

- As far as possible make the electric potential of your work clothes and that of the work bench the ground potential.

- To reduce the generation of static electricity be careful that the air in the work is not too dried. A relative humidity of 50%-60% is recommended.

### 7.5 Precaution for Soldering to Eastrising LCM

- Observe the following when soldering lead wire, connector cable and etc. to the LCM.

- -Soldering iron temperature: 280°C±10°C

- -Soldering time: 3-4 sec.

- -Solder: eutectic solder.

If soldering flux is used, be sure to remove any remaining flux after finishing to soldering operation. (This does not apply in the case of a non-halogen type of flux.) It is recommended that you protect the LCD surface with a cover during soldering to prevent any damage due to flux spatters.

- When soldering the electroluminescent panel and PC board, the panel and board should not be detached more than three times. This maximum number is determined by the temperature and time conditions mentioned above, though there may be some variance depending on the temperature of the soldering iron.

- When remove the electroluminescent panel from the PC board, be sure the solder has completely melted, the soldered pad on the PCs board could be damaged.

#### 7.6 Precaution for Operation

- Driving the Eastrising LCD in the voltage above the limit shortens its life.

- Response time is greatly delayed at temperature below the operating temperature range. However, this does not mean the LCD will be out of the order. It will recover when it returns to the specified temperature range.

- If Eastrising display area is pushed hard during operation, the display will become abnormal. However, it will return to normal if it is turned off and then back on.

- Condensation on terminals can cause an electrochemical reaction disrupting the terminal circuit. Therefore, it must be used under the relative condition of 40°C, 50% RH.

- When turning the power on, input each signal after the positive/negative voltage becomes stable.

URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 24 of 27

#### 7.7 Limited Warranty

Unless agreed between Eastrising and customer, Eastrising will replace or repair any of its LCD modules which are found to be functionally defective when inspected in accordance with Eastrising LCD acceptance standards (copies available upon request) for a period of one year from date of shipments. Cosmetic/visual defects must be returned to Eastrising within 90 days of shipment. Confirmation of such date shall be based on freight documents. The warranty liability of Eastrising limited to repair and/or replacement on the terms set forth above. Eastrising will not be responsible for any subsequent or consequential events.

#### 7.8 Return Policy

No warranty can be granted if the precautions stated above have been disregarded. The typical examples of violations are:

- -Broken LCD glass.

- -PCB eyelet damaged or modified.

- -PCB conductors damaged.

- -Circuit modified in any way, including addition of components.

- -PCB tampered with by grinding, engraving or painting varnish.

- -Soldering to or modifying the bezel in any manner.

Module repairs will be invoiced to the customer upon mutual agreement. Modules must be returned with sufficient description of the failures or defects. Any connectors or cable installed by the customer must be removed completely without damaging the PCB eyelet's, conductors and terminals.

URL: <a href="www.buydisplay.com">www.buydisplay.com</a> Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 25 of 27

### 8. IMAGE STICKING

#### 8.1 What is Image Sticking?

If you remain a fixed image on LCD Display for a long period of time, you may experience a phenomenon called Image Sticking. Image Sticking - sometimes also called "image retention" or "ghosting" - is a phenomenon where a faint outline of a previously displayed image remains visible on the screen when the image is changed. It can occur at variable levels of intensity depending on the specific image makeup, as well as the amount of time the core image elements are allowed to remain unchanged on the screen. In POS applications, for example, a button menu which remains fixed, or in which the "frame" elements (core image) remain fixed and the buttons may change, may be susceptible to image sticking. It is important to note that if the screen is used exclusively for this application, the user may never notice this phenomenon since the screen never displays other content. It is only when an image other than the "retained" image is shown on the screen that this issue becomes evident. Image sticking is different that the "burn-in" effect commonly associated with phosphor based devices.

#### 8.2 What causes Image Sticking?

Image sticking is an intrinsic behavior of LCD displays due to the susceptibility to polarization of the interior materials (liquid crystals) when used under static, charged conditions (continuously displaying the same image). The individual liquid crystals in an LCD panel have unique electrical properties. Displaying a fixed pattern - such as the POS menu described above – over prolonged periods can cause a parasitic charge build-up (polarization) within the liquid crystals which affects the crystals' optical properties and ultimately prevents the liquid crystal from returning to its normal, relaxed state when the pattern is finally changed. This effect takes place at a cellular level within the LCD, and the effect can cause charged crystal alignment at the bottom or top of a crystal cell in the "z" axis, or even crystal migration to the edges of a cell, again based on their polarity. These conditions can cause image sticking over an entire area, or at boundaries of distinct color change respectively. In either case, when the liquid crystals in the pixels and sub-pixels utilized to display the static image are polarized such that they can not return fully to their "relaxed" state upon deactivation, the result is a faint, visible, retained image on the panel upon presentation of a new, different image. The actual rate of image retention depends on variation factors such as the specific image, how long it is displayed unchanged, the temperature within the panel and even the specific panel brand due to manufacturing differences amongst panel manufacturers.

URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553 Datasheet Page: 26 of 27

#### 8.3 How to Avoid Image Sticking?

- Try not to operate the LCD with a "fixed" image on the screen for more than 2 hours.

- If you are operating the monitor in an elevated temperature environment and with a displayed image which is contrary to the recommendations in "For Software Developers" below, image stick can occur in as little as 30 minutes. Adjust your screen saver settings accordingly.

- Power down the unit during prolonged periods of inactivity such as the hours a store is closed or a shift during which the piece of equipment isn't used.

- Use a screensaver with a black or medium gray background that is automatically set to come on if the device is inactive for more than 5-10 minutes.

- Avoid placing the monitor in poorly ventilated areas or in areas that will create excess heat around the monitor for software developers.

- In defining the icons, buttons, or windows in the screen, try to utilize block patterns instead of distinct lines as borders for dividing the display into distinct areas.

- If it is necessary to display a static image, try to use colors that are symmetric to the middle grey level at the boundary of two different colors, and slightly shift the borders line once in a while.

- Try to utilize medium gray hues for those areas that will have prolonged display times or remain static as other menu elements change.

#### 8.4 How to Fix the Image Sticking?

Unlike the usually irreversible "burn-in" effects commonly associated with direct view phosphor display devices such as CRTs, an image retained on an LCD display can be reversed – often to a point of total invisibility. However, the severity of the underlying causes (as described above) of the image retained on a specific display, as well as the variation factors (see "For Software Developers" above) under which the retained image was created, will dictate the final level of retention reversal. One way to erase a retained image on a panel is to run the screen (monitor "on") in an "all black" pattern for 4-6 hours. It is also helpful to do this in an elevated temperature environment of approximately 35° to 50°C. Again, utilizing a dynamic screen saver with an all black background during prolonged idle display periods is a good way to avoid image retention issues.

#### 8.5 Is Image Sticking Covered by Eastrising RMA Warranty?

Image sticking is a phenomenon inherent to LCD Display technology itself, and as such, the occurrence of this "ghosting" effect is considered normal operation by the manufacturers of the LCD display modules which are integrated into today's monitor solutions. Eastrising does not warrant any display against the occurrence of image sticking. We strongly advise that you follow the operating recommendations listed above to avoid the occurrence of this phenomenon.

That's the end of the datasheet.

URL: www.buydisplay.com Document Name: ER-TFT101B4-1-5553\_Datasheet Page: 27 of 27